## AME 3623: Embedded Real-Time Systems: Final Exam

## Solution Set

May 13, 2009

| Problem | Topic                 | Max | Grade |

|---------|-----------------------|-----|-------|

| 0       | Name                  | 2   |       |

| 1       | Interrupts and I/O    | 45  |       |

| 2       | Finite State Machines | 60  |       |

| 3       | Sequential Logic      | 35  |       |

| 4       | Analog Processing     | 10  |       |

| 5       | Microprocessor Design | 30  |       |

| 6       | Logic                 | 20  |       |

| Total   |                       | 202 |       |

### 1. Interrupts and I/O

(a) (15 pts) Below is an interrupt service routine that is supposed to produce a signal of 50% duty cycle and a varible period on portD, pin 6. However, there exist several bugs (errors). Make the necessary changes to this code to remove these bugs. The number of counts for each "half cycle" is specified by the variable duration (i.e., for a single cycle, the pin should be 1 for duration counts and then 0 for another duration counts). You may assume that the I/O hardware has been initialized correctly.

```

volatile uint8_t duration;

ISR(TIMER0_OVF_vect) {

static uint8_t counter = 0xff;

++counter;

if(counter <= duration) {

PIND &= 0x80;

}

}

```

The repaired code is as follows:

```

volatile uint8_t duration;

ISR(TIMER0_OVF_vect) {

static uint8_t counter = 0xff;

++counter;

if(counter == duration) {

PORTD ^= 0x40;

counter = 0;

}

}

```

Key changes:

- Use XOR instead of AND

- bit 6 mask is 64 (or 0x40)

- counter == duration

- (b) (5 pts) Assume that the code above has been corrected. Given a prescaler of 8 and duration = 40, what is the resulting interrupt frequency? (set up the fraction, but do not reduce it)

$\frac{16,000,000}{8*256}$  Hz

(c) (5 pts) Given a prescaler of 8 and *duration* = 15, what is the frequency of the signal produced on the PORTD output pin? (again, set up the fraction, but do not reduce it)

$\frac{16,000,000}{8*256*15*2}~Hz$

(d) (5 pts) (True/False) In the Atmel Mega8, the highest overflow interrupt frequency of timer 0 is less than the highest interrupt frequency of timer 1. Explain.

False. The highest frequency of timer 1 is 256 times less than that of timer 0 (due to the fact that it is a 16-bit counter, as opposed to an 8-bit counter).

```

uint16_t get(void) {

uint16_t val = 0;

char c;

while(1) {

c = getchar();

if('0' <= c && c <= '9'){

val = val * 16 + c - '0';

}else if('a' <= c && c <= 'f'){

val = val * 16 + c - 'a' + 10;

}else{

return(val);

}

}</pre>

```

(e) (5 pts) What does the function **get()** do when the following characters are sent through the serial port: '5', '\n'?

It returns the value 0x5 (or decimal 5).

(f) (5 pts) What does the function **get()** do when the following characters are sent through the serial port: '5', 'e', '\n'?

It returns the value 0x5e (or decimal 94).

(g) (5 pts) Explain what the function **get()** does in general. Be brief.

This function accepts a multi-character hexadecimal number and returns its value. (It can handle up to 4 bytes)

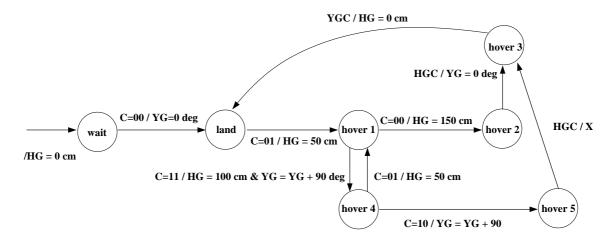

### 2. Finite State Machines

Consider a finite state machine controller of a helicopter not unlike the ones that we used for our projects. This controller has access to the following actions:

- HG = xxx cm. Set the height goal to xxx. You may assume that the underlying PID controller will eventually bring the height to the currently set goal.

- YG = yyy deg. Set the yaw goal to yyy. The associated PID controller will eventually bring the true yaw to the yaw goal.

- X. Do nothing

The FSM also has the following events:

- HGC. Height goal complete. The helicopter has reached its height goal.

- YGC. Yaw goal complete.

- C = bb. A control input that can be one of four different values: 00, 01, 10 or 11 (so, 4 different events). This control input is set by some remote pilot.

The FSM is as follows:

Assume that events that are not listed result in the FSM remaining in the current state.

(a) (5 pts) Starting from the *wait* state, assume that the following commands are issued in this order: 00, 01, 00. What is the state that the FSM stops in?

The land state.

(b) (5 pts) What is the orientation of the heli at this state?

Zero degrees.

- (c) (5 pts) What is the maximum height obtained by the heli during the sequence?150cm.

- (d) (5 pts) Starting from the *wait* state, assume that the following commands are issued in this order: 00, 01, 11, 10. What is the state that the FSM stops in?

The land state.

(e) (5 pts) What is the orientation of the heli at this state?

180 degrees.

- (f) (5 pts) What is the maximum height obtained by the heli during the sequence?100cm.

- (g) (10 pts) What sequence of commands would result in a landing orientation of 270 degrees?

00, 01, 11, 01, 11, 10

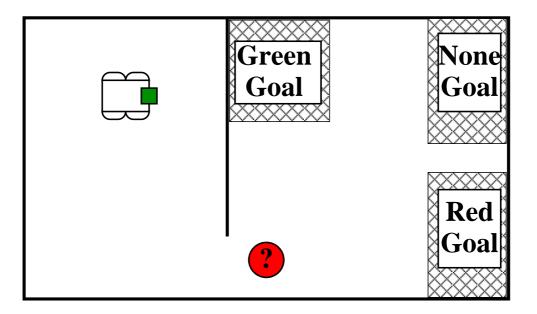

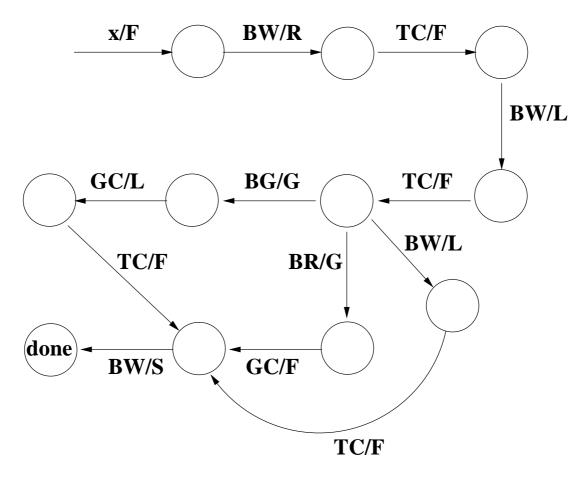

Consider the following robot world in which the mobile robot is facing to the right.

The robot is able to execute the following actions:

- Move forward (F): continues to move forward until another action is issued

- Stop (S)

- Turn left (L): initiate a turn to the left. This turn will complete exactly at 90 degrees

- Turn right (R)

- Grasp (G): grasp an object that is in front of the robot

The robot is sensitive to the following events:

- Bump Wall (BW): bumped into a wall

- Bump Red Ball (BR): bumped into a red ball

- Bump Green Ball (BG): bumped into a green ball

- Turn complete (TC)

- Grasp complete (GC)

Your task is to design a finite state machine that takes the robot from its current position to one of the goal locations. If the robot runs into a ball along the way, it should also grasp it and carry it to the corresponding goal. If it does not encounter a ball, then the robot should stop in the *None goal* region. Note: the ball can only occur at the designated location.

(h) (20 pts) Draw the finite state machine diagram that will control the robot through this sequence. Note that your FSM should perform properly in all three cases.

# 3. Sequential Logic

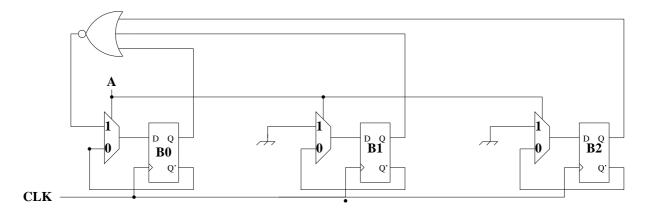

Consider the following circuit:

(a) (15 pts) Fill in the following truth table:

| A | $B_2$ | $B_1$ | $B_0$ | $D_2$ | $D_1$ | $D_0$ |

|---|-------|-------|-------|-------|-------|-------|

| 0 | 0     | 0     | 0     | 1     | 1     | 1     |

| 0 | 0     | 0     | 1     | 1     | 1     | 0     |

| 0 | 0     | 1     | 0     | 1     | 0     | 1     |

| 0 | 0     | 1     | 1     | 1     | 0     | 0     |

| 0 | 1     | 0     | 0     | 0     | 1     | 1     |

| 0 | 1     | 0     | 1     | 0     | 1     | 0     |

| 0 | 1     | 1     | 0     | 0     | 0     | 1     |

| 0 | 1     | 1     | 1     | 0     | 0     | 0     |

| 1 | 0     | 0     | 0     | 0     | 0     | 1     |

| 1 | 0     | 0     | 1     | 0     | 0     | 0     |

| 1 | 0     | 1     | 0     | 0     | 0     | 0     |

| 1 | 0     | 1     | 1     | 0     | 0     | 0     |

| 1 | 1     | 0     | 0     | 0     | 0     | 0     |

| 1 | 1     | 0     | 1     | 0     | 0     | 0     |

| 1 | 1     | 1     | 0     | 0     | 0     | 0     |

| 1 | 1     | 1     | 1     | 0     | 0     | 0     |

|   |       |       |       |       |       |       |

(35 pts)

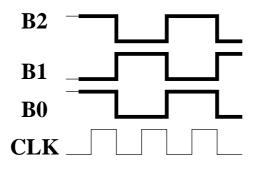

(b) (5 pts) Assuming that A = 0 and an initial state of  $B_2, B_1, B_0 = 101$ , fill in the following timing diagram:

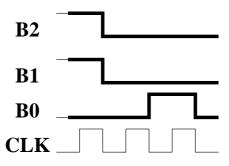

(c) (5 pts) Assuming that A = 1 and an initial state of  $B_2, B_1, B_0 = 110$ , fill in the following timing diagram:

(d) (5 pts) Interpreting  $B_2, B_1, B_0$  as a 3-bit binary number, when A = 0, what mathematical operation does this circuit perform when the clock changes from high to low? Your answer should apply to all possible combination of bits.

This circuit performs a bit-wise NOT operation.

(e) (5 pts) When A = 1, what mathematical operation does this circuit perform when the clock changes from high to low?

This circuit performs a logical NOT operation.

## 4. Analog Processing

(10 pts)

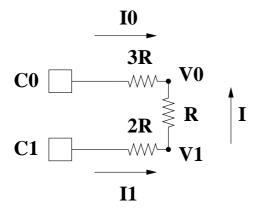

Consider the following digital-to-analog circuit:

(a) (10 pts) Derive an equation for  $V_1$  as a function of  $C_1$  and  $C_0$ . Show your work.

**The easy path:** We really don't care about what  $V_0$  is. So – we will treat 3R and R as one lumped resistor of resistance 4R. The essential equations are:

$$5C_0 - V_1 = 4RI_0 5C_1 - V_1 = 2RI_1 I_1 + I_0 = 0$$

So:

$$\frac{5C_0 - V_1}{4R} + \frac{5C_1 - V_1}{2R} = 0$$

$$5C_0 - V_1 + 10C_1 - 2V_1 = 0$$

$$V_1 = \frac{5}{3} (C_0 + 2C_1)$$

# The harder path: Explicitly handle both $V_0$ and $V_1$ .

The essential equations are:

$5C_0 - V_0 = 3RI_0 (1)$

$$5C_1 - V_1 = 2RI_1 (2)$$

$$V_1 - V_0 = RI \tag{3}$$

$$I_0 + I = 0 \tag{4}$$

$$I_1 = I \tag{5}$$

Combining equations 4 and 5:

$$I_0 + I_1 = 0 (6)$$

Combining equations 1, 3 and 4:

$$5C_0 - V_1 - RI = 3RI_0 5C_0 - V_1 = 4RI_0$$

(7)

Equations 7, 2, and 6 are the equations we start the easy path with.

#### 5. Microprocessor Design

(a) (5 pts) Briefly explain the function of the *chip select* signal for a memory chip.

The chip select must be active in order for the memory chip to do anything (read from or write to the bus). This control signal allows multiple chips to share the same set of address lines, and yet not interfere with one another.

(b) (5 pts) (True/False) The data line is an output from a memory chip. Explain.

True sometimes. It is only an output when we are reading from the memory chip. It can also be an input (if it is a RAM memory chip) and it often does nothing with the bus.

(c) (5 pts) (True/False) In the Atmel Mega8, PIND is a general purpose register. Explain.

False. This register controls the hardware that brings the current values on the port D pins onto the data bus.

(d) (5 pts) (True/False) The arithmetic logical unit receives arguments (values) from the general purpose registers. Explain.

True. This is the only way for arguments to be presented to the ALU. After computing the value, it also places the result into the general purpose registers.

(e) (10 pts) What is the value of variable *baz* at the end of this segment of code (in hexadecimal)?

foo = 0xe5;

bar = 135;

baz = foo & bar | 29;

baz = 0x9D

```

Here is the sequence:

bar = 0x87

bar & foo = 0x85

29 = 0x1D

0x1D | 0x85 = 0x9D

```

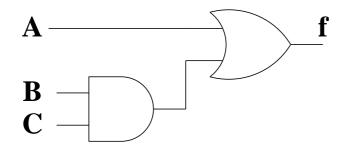

## 6. Logic

Given the following truth table:

| А | В | С | f |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

(a) (5 pts) Give the "minterm" form of the corresponding algebraic expression.

$f = \bar{A}BC + A\bar{B}\bar{C} + A\bar{B}C + AB\bar{C} + AB\bar{C}$

(b) (10 pts) Derive a simplified algebraic description for f. Justify each step (provide the name of the rule that you are using).

$\bar{A}BC + A\bar{B}\bar{C} + A\bar{B}C + AB\bar{C} + ABC$  $\bar{A}BC + A\bar{B}\bar{C} + A\bar{B}C + AB\bar{C} + ABC + ABC$ X + X = X $\bar{A}BC + ABC + A\bar{B}\bar{C} + A\bar{B}C + AB\bar{C} + ABC$ Commutative Law  $(\bar{A} + A)BC + A\bar{B}(\bar{C} + C) + AB(\bar{C} + C)$ Distributive Law  $1 * BC + A\bar{B} * 1 + AB * 1$  $X + \bar{X} = 1$  $BC + A\overline{B} + AB$ X \* 1 = X $BC + A(\bar{B} + B)$ Distributive Law  $X + \bar{X} = 1$ BC + A \* 1X \* 1 = XBC + A

(c) (5 pts) Draw the corresponding circuit.