Final Report for:

## Configuring Embeddable Adaptive Computing Systems for Multiple Application Domains with Minimal Size, Weight, and Power

DARPA Contract F30602-97-2-0297

Technical Point of Contact:

Dr. John K. Antonio, Director School of Computer Science University of Oklahoma 200 Felgar Street Norman, OK 73019-6151 fax: 405-325-4044 tel: 405-325-4397 <u>antonio@ou.edu</u> www.cs.ou.edu/~antonio

October 2002

## Abstract

A main objective of this effort was to demonstrate the advantages of integrating field programmable gate array (FPGA), digital signal processor (DSP), and general purpose processor (GPP) computing technologies together to perform computations required by embedded radar applications of interest to DARPA. Particular emphasis was placed on minimization of the overall size, weight, and power (SWAP) of the computational platform. To facilitate the practical use of integrated systems containing different types of computing technologies, configuration techniques and tools were developed for aiding the system designer in determining optimal specifications of system requirements for given instances of the applications considered. A prototype FPGA/DSP/GPP-based system was developed to illustrate the feasibility of the research.

# **Table of Contents**

| Abstract                                                                    | 2      |

|-----------------------------------------------------------------------------|--------|

| List of Figures                                                             |        |

| Acknowledgments                                                             |        |

| Introduction                                                                |        |

| Organizational Structure of the Report                                      | 9      |

| Project Overview                                                            |        |

| Brief Descriptions of Major Parts of the Report                             | 11     |

| Part 1: Optimal Multiprocessor Configuration for SAR                        |        |

| Overview of References [1A], [2B], and [3]                                  | 13     |

| Part 2: Optimal Communication Scheduling for STAP                           |        |

| Overview of References [4C], [5D], [6E], [7], and [8]                       |        |

| Part 3: FPGA Power Prediction and Applications                              |        |

| 3.1 FPGA Power Prediction                                                   |        |

| Overview of References [9F] and [10]                                        | 20     |

| Overview of Reference [11G]                                                 |        |

| 3.2 FPGA Applications                                                       | 22     |

| Overview of References [12H] and [13]                                       | 22     |

| Overview of Reference [14]                                                  |        |

| Overview of Reference [15]                                                  |        |

| Overview of References [16J] and [17]                                       |        |

| Part 4: Hybrid FPGA/DSP/GPP Platform.                                       |        |

| Overview of Reference [18K]                                                 | 27     |

| Conclusion                                                                  |        |

| Technology Transfer                                                         | 41     |

| Deliverables                                                                | 41     |

| References                                                                  | 43     |

| Additional Materials                                                        |        |

| List of Acronyms                                                            | 47     |

| Appendix A: Jeffrey T. Muehring and John K. Antonio, "Optimal Configurat    |        |

| Embedded Parallel System for Synthetic Aperture Radar Processing," Procee   |        |

| International Conference on Signal Processing Applications & Technology, H  | 0 0    |

| Oct. 1996, pp. 1489-1494.                                                   |        |

| Appendix B: Jeffrey T. Muehring and John K. Antonio, "Optimal Configuration | ion of |

| Compute Nodes for Synthetic Aperture Radar Processing," Proceedings of th   |        |

| International Workshop on Embedded HPC Systems and Applications (EHPC       |        |

| Lecture Notes in Computer Science 1388: Parallel and Distributed Processin  |        |

| Jose Rolim, sponsor: IEEE Computer Society, Orlando, FL, USA, Apr. 1998,    | • •    |

| 993                                                                         |        |

| Appendix C: Jack M. West and John K. Antonio, "Simulation of the Commun     |        |

| Time for a Space-Time Adaptive Processing Algorithm on a Parallel Embedd    |        |

| Proceedings of the International Workshop on Embedded HPC Systems and       | •      |

| (EHPC '98), in Lecture Notes in Computer Science 1388: Parallel and Distri  | 11     |

|                                                                             |        |

| <i>Processing</i> , edited by Jose Rolim, sponsor: IEEE Computer Society, Orlando, FL, USA, Apr. 1998, pp. 979-986                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix D: Jack M. West and John K. Antonio, "A Genetic Algorithm Approach to<br>Scheduling Communications for a Class of Parallel Space-Time Adaptive Processing<br>Algorithms," <i>Proceedings of the 5<sup>th</sup> International Workshop on Embedded/Distributed</i><br><i>HPC Systems and Applications (EHPC 2000)</i> , in <i>Lecture Notes in Computer Science</i> ,<br><i>IPDPS 2000 Workshops</i> , sponsor: IEEE Computer Society, Cancun, Mexico, May 2000,<br>pp. 855-861                                                                     |

| Appendix E: Jack M. West and John K. Antonio, "A Genetic-Algorithm Approach to<br>Scheduling Communications for Embedded Parallel Space-Time Adaptive Processing<br>Algorithms," <i>Journal of Parallel and Distributed Computing</i> , Vol. 62, No. 9, Sept. 2002,<br>pp. 1386-1406                                                                                                                                                                                                                                                                        |

| Appendix F: Timothy Osmulski, Jeffrey T. Muehring, Brian Veale, Jack M. West,<br>Hongping Li, Sirirut Vanichayobon, Seok-Hyun Ko, John K. Antonio, and Sudarshan K.<br>Dhall, "A Probabilistic Power Prediction Tool for the Xilinx 4000-Series FPGA,"<br><i>Proceedings of the 5<sup>th</sup> International Workshop on Embedded/Distributed HPC Systems</i><br><i>and Applications (EHPC 2000)</i> , in <i>Lecture Notes in Computer Science, IPDPS 2000</i><br><i>Workshops</i> , sponsor: IEEE Computer Society, Cancun, Mexico, May 2000, pp. 776-783. |

| Appendix G: Hongping Li, John K. Antonio, and Sudarshan K. Dhall, "Fast and Precise<br>Power Prediction for Combinational Circuits," <i>Proceedings of the IEEE Symposium on</i><br><i>VLSI</i> , sponsor: IEEE, Tampa, FL, Feb 2003, pp. 254-259                                                                                                                                                                                                                                                                                                           |

| Appendix I: Jeffrey T. Muehring and John K. Antonio, "Minimizing Power Consumption<br>using Signal Activity Transformations for Very Deep FPGA Pipelines," <i>Proceedings of</i><br><i>the Military and Aerospace Applications for Programmable Devices and Technologies</i><br><i>Conference (MAPLD 2000)</i> , sponsors: NASA and Johns Hopkins University/Applied<br>Physics Laboratory, Laurel, MD, Sep. 2000                                                                                                                                           |

| Appendix K: Jack M. West, Hongping Li, Sirirut Vanichayobon, Jeffrey T. Muehring,<br>John K. Antonio, and Sudarshan K. Dhall, "A Hybrid FPGA/DSP/GPP Prototype<br>Architecture for SAR and STAP," <i>Proceedings of the Fourth Annual High Performance</i><br><i>Embedded Computing Workshop</i> , sponsors: U.S. Navy and Defense Advanced Research<br>Projects Agency (DARPA), MIT Lincoln Laboratory Publications, Group 18, Lexington,<br>MA, Sep. 2000, pp. 29-30                                                                                      |

# List of Figures

| Figure 1. Organizational structure of the report.                                  | 9        |

|------------------------------------------------------------------------------------|----------|

| Figure 2. This diagram illustrates the method of performing sectioned fast convolu | tions    |

| on azimuth input data with a pre-stored kernel. Given that the kernel size is fix  | æd,      |

| then if the section size is made large, a relatively small fraction of samples are |          |

| discarded for each section, thus making processor efficiency high. Conversely      | , if the |

| section size is small, then a relatively large fraction of samples must be discard | led for  |

| each section, resulting in poor processor efficiency, but relatively small memo    | ry       |

| requirements.                                                                      | 14       |

| Figure 3. Optimal CN Configurations of the CN-constrained Model [2B]               | 16       |

| Figure 4. Measured power consumption of the configuration files and data sets from | m [9F].  |

|                                                                                    | 22       |

| Figure 5. Structure of the deep pipeline                                           |          |

| Figure 6. Using activity transformations to minimize power consumption             |          |

| Figure 7. Block diagram of the FPGA/DSP/GPP prototype architecture                 | 28       |

| Figure 8. Detail of the FPGA/DSP/GPP prototype architecture                        | 29       |

| Figure 9. Photograph of the FPGA/DSP/GPP prototype architecture                    | 30       |

| Figure 10. Interface Design: Communication from Annapolis FPGA (F) to Mercur       | y31      |

| Figure 11. Interface Design: Communication from Mercury to Annapolis FPGA (E       | 3)32     |

| Figure 12. Illustration of how the major computational components of SAR proces    | sing     |

| can be mapped onto the hybrid system.                                              | 32       |

| Figure 13. Illustration of how the major computational components of STAP proc     | essing   |

| can be mapped onto the hybrid system.                                              | 33       |

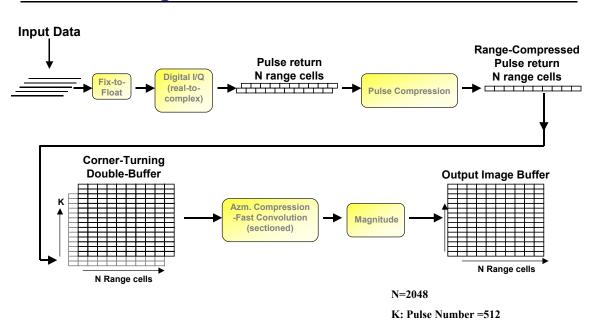

| Figure 14. Figure 14. SAR Processing Flow.                                         | 33       |

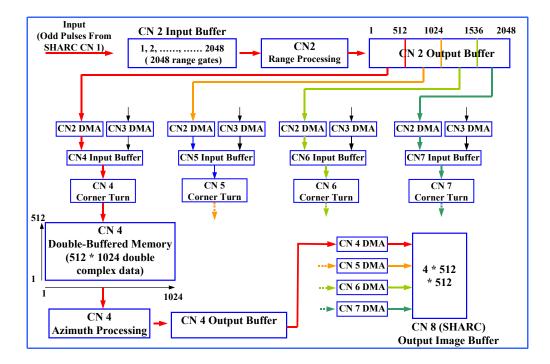

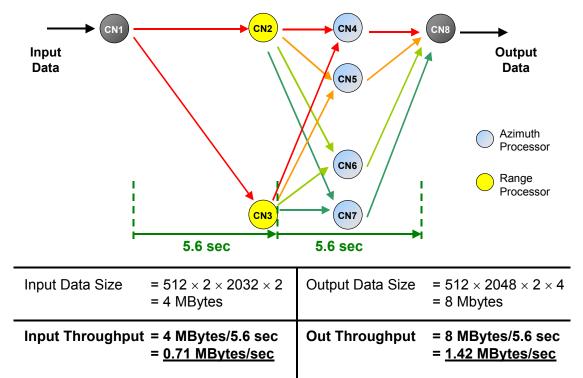

| Figure 15. Data distribution for Parallel SAR Processing on Mercury.               | 34       |

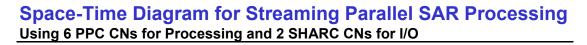

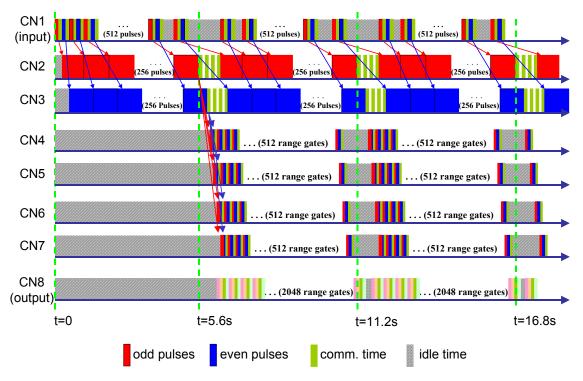

| Figure 16. Space-time diagram for streaming parallel SAR processing                | 35       |

| Figure 17. Throughput requirements achieved for streaming parallel SAR processi    | ng36     |

| Figure 18. Streaming parallel RT_STAP on Mercury Subsystem                         | 37       |

| Figure 19. Parallel RT_STAP on Mercury Subsystem.                                  | 38       |

| Figure 20. Space-time diagram for parallel RT_STAP.                                |          |

| Figure 21. Throughput requirements achieved for the medium case parallel RT_ST     | AP.40    |

## Acknowledgments

I would first like to acknowledge and thank the graduate students that worked on this project. Every publication associated with the project was co-authored with one or more graduate assistants and was based on research conducted in conjunction with a PhD dissertation or MS thesis.

Jeff Muehring (initially an MS student and later a PhD student) conducted research in the area of determining optimal configurations for SAR (synthetic aperture radar) processing. His work included the application of mathematical programming techniques for determining optimal multiprocessor configurations for SAR. His techniques centered on the concept of making the proper trade-off between processing hardware and memory so as to minimize the overall power consumption of the system, while satisfying throughput requirements. Jeff also made contributions in the domain of FPGA (field programmable gate array) design by proposing a new way of implementing twodimensional signal processing tasks (including SAR) using very deep FPGA pipelines. In addition, Jeff played an important role in designing and implementing the hardware portions of the custom interfaces between the FPGA and DSP/GPP subsystems of the constructed prototype platform.

Jack West (initially an MS student and later a PhD student) conducted research in the area of minimizing communication time for STAP (space-time adaptive processing) executing on a multiprocessor. By minimizing communication overhead, he demonstrated that less hardware is required for given instances of STAP, thereby reducing SWAP (size, weight, and power). The first phase of Jack's work included the development of a simulator for Mercury's RACEway® interconnection network. This fast and efficient simulator was used in the second phase of his work in which genetic algorithm approaches were developed for solving the communication scheduling problem. Jack also played important roles in developing the prototype system by helping with the STAP application software implementation and by designing and implementing the software portions of the custom interfaces connecting the FPGA and DSP/GPP subsystems.

Tim Osmulski (MS student) developed and implemented an analytical tool, in software, for estimating power consumption of a configured FPGA chip. This tool, which was the first of its kind, demonstrated that it is indeed possible to accurately predict FPGA power consumption by applying existing analytical approaches. The accuracy of Tim's tool was verified by comparing its predicted values with actual measured power consumption taken from an instrumented FPGA board.

Hongping Li (PhD student) developed a new analytical approach for estimating power consumption of circuits, including those implemented on a FPGA. His approach is based on a Markov chain signal model, and directly accounts for correlations present among the internal signals of the circuit. Hongping verified the accuracy of his approach using PSpice® based simulation studies. Hongping also lead the effort in implementing the parallel SAR application software on the multiprocessor system.

Nikhil Gupta (MS student) developed FPGA circuit designs to support core calculations required by STAP. His work demonstrated that 16-bit block floating point

arithmetic provides acceptable accuracy for many situations. The advantage of using block floating point arithmetic, instead of standard floating point, is the significant reduction in the size and power consumption of the corresponding circuits. His research illustrated that if the values of the input data are approximately uniformly distributed, then the block floating point approach delivers acceptable accuracy.

Brian Veale (initially an MS student and later a PhD student) conducted a study comparing different FPGA designs and implementations for an inner product coprocessor. He studied two architectural approaches for the co-processor and two different types of arithmetic (integer and floating point) for a total of four combinations. For each implementation, he also studied the effect that employing different degrees of pipelining had on each design in terms of size, speed, and power consumption. His study of pipelining resulted in some counterintuitive results. In particular, while it is well known that increasing the degree of pipelining generally enables custom designs to be run at faster clock rates, the same is not always true for FPGA designs.

Sirirut Vanichayobon (PhD student) studied the power-speed trade-off for a class of circuits known as prefix circuits. These circuits are important in their own right, and are representative of the type of circuit often required in high-performance embedded applications. Through extensive analysis of a number of known prefix circuits, her work illustrates that the trade-off between power and speed is not always obvious to the circuit designer. Based on discoveries made through her research, some important guidelines for properly matching circuit characteristics with power and speed requirements are provided. Sirirut also lead the effort in implementing the parallel STAP application software on the multiprocessor system.

I would also like to acknowledge the work and contributions of faculty colleagues. Dr. Sudarshan Dhall served as co-PI on this project since the Fall of 1999; the time at which I became Director of Computer Science at the University of Oklahoma. Dr. Dhall made contributions in nearly all aspects of the project, and was particularly instrumental in guiding the research of graduate assistants Sirirut Vanichayobon and Hongping Li. Dr. Dhall's expertise in system modeling – and probabilistic techniques in particular – was extremely valuable. The project also benefited greatly by the contributions of Dr. S. Lakshmivarahan. It was Dr. Lakshmivarahan that originally proposed the topic of Sirirut's research, and he and Dr. Dhall served as co-advisors of her PhD committee.

Next, I would like to acknowledge the assistance and guidance of key defense personnel, starting with Rick Metzger of Rome Laboratory. Rick served as program manager for a related prior project I performed for Rome Laboratory, and it was this past work experience that enabled me to be successful in proposing and completing the present project for DARPA.

I would like to acknowledge the support and encouragement of José Muñoz, who served as the original program manager for DARPA's ACS (Adaptive Computing Systems) program. José provided valuable feedback and perspective throughout the contract period. I had the opportunity to meet with José and his staff frequently, including at annual reviews, PI meetings, and other professional conferences. He actively encouraged and facilitated interaction and collaboration among the PIs of different projects, which ensured that the ACS program was cohesive and integrated. The interactions with other PIs was stimulating, and served to accelerate and improve the quality and relevance of the results delivered by all project PIs.

Assisting José Muñoz with the management of this project was Ralph Kohler of Rome Laboratory. I met with Ralph on a regular basis at meetings and conferences and communicated with him frequently through e-mail and telephone correspondence. Ralph made a number of technical contributions and refinements to the project, and often served as a sounding board on behalf of the military. He related to me the actual needs of the war fighter, and these insights helped us to provide results that were more applicable than would have otherwise been possible. Ralph also helped me tremendously with the overall management and organization of the project.

Finally, I would like to thank Jules Bergmann of Rome Laboratory, who had the unenviable task of encouraging me to complete and submit this final report. Jules was most gracious and professional; he gently, but persistently, encouraged me to finish this report. I would not want to think when this report would have been delivered without the interaction and encouragement provided by Jules.

## Introduction

## Organizational Structure of the Report

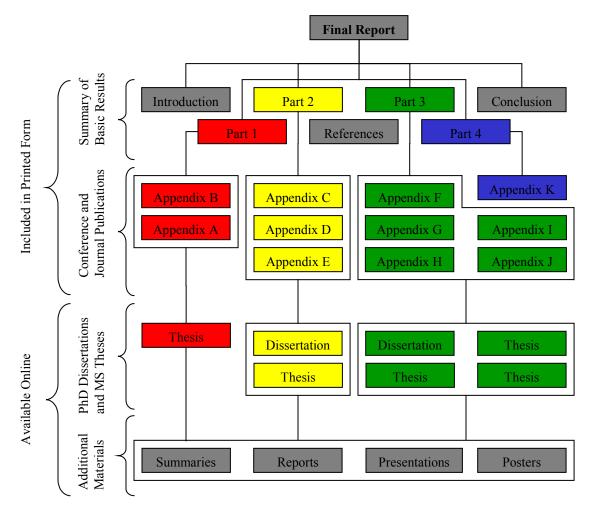

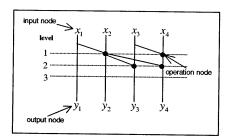

A challenge in organizing this report was to provide sufficient detail to readers that desire it, while also providing a relatively high-level summary of the entire project. Published materials that resulted from this project currently include eleven conference/journal papers, two PhD dissertations, and five MS theses. The eleven published papers are included in printed form in the appendices of this report. It was natural to include copies of the papers in printed form and refer readers interested in further details to the dissertations and theses (which are available online) because the papers were generally derived from the dissertations and theses. It was infeasible to incorporate the dissertations and theses in printed form; there are over 800 pages associated with these documents. The report is organized hierarchically, as illustrated in Figure 1.

Figure 1. Organizational structure of the report.

The main body of the report provides a summary of basic results, and includes four major parts: (1) Optimal Multiprocessor Configuration for SAR; (2) Optimal Communication Scheduling for STAP; (3) FPGA Power Prediction and Applications; and (4) Hybrid FPGA/DSP/GPP Platform. Each of these parts is supported by a collection of published papers, theses, and dissertations produced during the project period. Copies of the published papers are included in the appendices of the report. References to these publications are labeled with a number followed by the letter of the appendix where a copy of the publication can be found. For example, reference label [1A] indicates that a copy of the referenced publication can be found in Appendix A. Due to size considerations, copies of theses and dissertations, such as reference [3], are not included in an appendix; however, online links for all references are provided in the list of references. For conference papers, links to the associated presentation materials are also provided within the list of references. As illustrated in Figure 1, additional materials are also available online, including annual project summaries, technical reports, and presentations and posters given at conferences and PI (principal investigator) meetings. Online links to additional materials are provided in the section entitled Additional Materials, which follows the References section.

Each major part is divided into subsections, and each subsection provides an overview of one or more published papers. Overviews of some of the conference papers (e.g., [15I] and [18K]) actually expand upon the publication by including content from the presentation materials associated with that publication. Readers not needing the level of detail found in these overviews are encouraged to first read the Acknowledgments section, which includes a paragraph on the work conducted by each student assistant. Of course readers requiring more detail are encouraged to pursue copies of the papers found in the appendices, online links of presentation materials found in the References section, and/or the online links found in the Additional Materials section.

#### Project Overview

The advantages of using digital signal processing (DSP) chips for high-performance embedded signal processing applications have been demonstrated during the past decade. DSP chips often win over general purpose processors (GPPs) because their complexity (measured, for example, in terms of silicon area, number of transistors, or power consumption) is better matched to the highly regular and numerical-intensive computations required by many signal processing based embedded applications. However, it is now apparent that even DSP chips can be overkill for some computations found in common embedded military applications. That is, in some cases DSP chips are equipped with much more architectural complexity than is actually needed, resulting in inefficiencies and greater power consumption than absolutely necessary.

In this project, we investigated the advantages of integrating configurable hardware together with a multiprocessor DSP/GPP platform. The computational engine of the configurable hardware used in this project was comprised of FPGA chips. A primary goal of our project was to demonstrate that for given computational loads – associated with instances of embedded radar signal processing applications – the total size, weight, and

power (SWAP) could be reduced by integrating FPGA-based components as part of the embedded computational platform.

Reconfigurable computing devices, such as FPGAs, can offer a cost-effective and more flexible alternative than the use of application specific integrated circuits (ASICs). FPGAs are especially cost-effective compared to ASICs when only a small number of the chip(s) are required. Another major advantage of FPGAs over ASICs is that they can be reconfigured to change their functionality while still resident in the system, which allows hardware designs to be changed similar to software, and dynamically reconfigured to perform different functions at different times.

A number of theoretical and empirical studies were conducted during the project period to understand and demonstrate the advantages and disadvantages of DSP/GPP versus FPGA technologies with respect to SWAP. A prototype heterogeneous FPGA/DSP/GPP-based platform was constructed using commercial off-the-shelf (COTS) components to demonstrate the utility of a hybrid system containing all three types of technologies. A number of systematic approaches and tools based on mathematical programming and modeling were developed to optimally configure FPGA/DSP/GPP-based platforms for applications in the radar signal-processing domain. The two major applications considered were SAR (synthetic aperture radar) and STAP (space-time adaptive processing).

The prototype system was constructed using COTS components from two vendors: Annapolis Micro Systems, Inc. and Mercury Computer Systems, Inc. We had excellent support from both companies, and we designed and implemented a custom interface to allow communication between two disparate product lines of these vendors. Implementation of a custom interface was necessary because at that time (1997-98) there were few interfacing standards among vendors such as the two we were working with and little customer demand (excluding us, of course!) for providing such an interface. The availability of products and support to more easily interface components from different vendors, including the two we worked with, is much better today. In fact, the output of our research, which illustrated the potential benefits of a hybrid FPGA/DSP/GPP platform, served as a catalyst for these industry sectors to invest significant resources and provide support and standards appropriate for interfacing their product lines.

## Brief Descriptions of Major Parts of the Report

Part 1: Optimal Multiprocessor Configuration for SAR – describes research for determining optimal multiprocessor configurations for instances of the SAR processing problem. The research was targeted at how to optimally configure a multiprocessor system for given instances of the SAR problem so that the resulting power consumption of the multiprocessor system is minimized. The key to the approach involved making the proper trade-off between the number of processors and amount of memory associated with the multiprocessor configuration. References associated with this work are [1A], [2B], and [3].

Part 2: Optimal Communication Scheduling for STAP – describes research for determining how to best schedule inter-processor communications of a parallel STAP algorithm mapped onto a Mercury Race Multiprocessor. The approach is based on a genetic algorithm, and the research also resulted in the development of a fast and accurate network simulator for the RACEway® interconnection network. References associated with this work are [4C], [5D], [6E], [7], and [8].

Part 3: FPGA Power Prediction and Applications – describes mathematical models and other approaches developed for predicting power consumption for FPGA circuits. We found that predicting power consumption for FPGAs was particularly difficult, as it strongly depends on precisely how the chip is configured and the "activity" characteristics of the input data being processed. Nevertheless, we generated new and important results and tools in this area. We also demonstrated the utility of using FPGA circuits for portions of the SAR and STAP applications. References associated with this work are [9F], [10], [11G], [12H], [13], [14], [15I], [16J], and [17].

Part 4: Hybrid FPGA/DSP/GPP Platform – describes a prototype hybrid platform that was constructed for this project. It includes the detailed design and development of the custom interfaces implemented to interconnect the disparate products of the two vendors. Some performance results are also included. The reference associated with this work is [18K].

## Part 1: Optimal Multiprocessor Configuration for SAR

## Overview of References [1A], [2B], and [3]

The real-time embedded application considered in this part, i.e., SAR, as well as many others of military interest, are characterized by a common theme: processing a continuous stream of data collected from radar sensors. The rate at which data samples flow from the sensor(s) to the computational platform is typically very high – often on the order of tens or hundreds of millions of samples per second and even higher. Furthermore, the number of calculations to be performed on each sample is typically at least 100 FLOPs (floating-point operations), which amounts to an overall computational throughput requirement ranging from at least one to ten billion FLOPs (and often much higher).

At the beginning of the contract period, approaches capable of providing a computational platform that could achieve these types of computational throughput rates typically involved a "pipeline of interconnected processors" style of architecture. Such an approach could be a valid and effective architecture in some cases. However, situations often arose in which the throughput requirements dictated that 100 or more SHARC® (or similar) DSP processors were required. In many situations, the associated level of power requirement for the computational platform alone posed a severe problem, because of the strict power budgets available on UAVs (unmanned aerial vehicles) and satellites where these systems are deployed.

In the paper [1A], we showed how a DSP/GPP-based multiprocessor system could be optimally configured using two types of processor/memory daughtercards to minimize overall power consumption for SAR applications. We showed that by careful (and often counterintuitive) selection of parameters associated with both the hardware (the number of daughtercards of two possible types) and the application software (a parameter known as the azimuth section size), an optimal configuration (one with minimal power consumption) can be derived based on the application of mathematical programming techniques.

Our approach centered on the derivation of two mathematical formulas for given instances of the SAR problem: one for the total numbers of processors required and the other for the total memory required. Both of these functions are dependent on the choice of the section size parameter. The derived functions dictate that if a small section size is used, then the associated memory requirements are small, but the processor requirements are high. On the other hand, a large section size was shown to result in a requirement for fewer processors, but more memory.

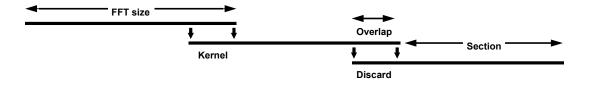

The reason a large section size implies that fewer processors are required is because only a small fraction of data is discarded during the calculation of the so-called sectioned fast convolutions (refer to Figure 2). This implies that the processors are being used with high efficiency when the section size is large. On the other hand, when a small section size is used, then more processors are required because a relatively large fraction of data is overlapped. From Figure 2, note that the overlapped data samples are actually processed twice. Although achieving high processor efficiency is a traditional objective, the trade-off is that implementing the associated large section sizes requires extra memory, and extra memory consumes extra power. It is this inherent trade-off between processor efficiency, memory, and section size that our approach optimized.

Large Overlap/Section ratio  $\Rightarrow$  Small azimuth memory, large number azimuth processors Small Overlap/Section ratio  $\Rightarrow$  Large azimuth memory, small number azimuth processors

Figure 2. This diagram illustrates the method of performing sectioned fast convolutions on azimuth input data with a pre-stored kernel. Given that the kernel size is fixed, then if the section size is made large, a relatively small fraction of samples are discarded for each section, thus making processor efficiency high. Conversely, if the section size is small, then a relatively large fraction of samples must be discarded for each section, resulting in poor processor efficiency, but relatively small memory requirements.

The two daughtercards assumed to be available in our approach were: Type 1, which had six SHARC® processors and a total of 32MB of memory; and Type 2, which had two SHARC® processors and a total of 64MB of memory. Thus, our optimization procedure was based on minimizing total consumed power based on proper selection of three parameters: section size, number of Type 1 cards, and number of Type 2 cards. Note that allowing two daughtercards in the configuration put additional constraints on the types of configurations that were possible. Thus, in general, arbitrary numbers of processors and amounts of memory could not me configured. However, the underlying concept of trading the efficiency of processors for more memory was still present.

One interesting lesson learned from our study happened when we considered a situation in which only Type 1 cards were assumed to be available for configuring the system (recall that the Type 1 card is "processor rich" and "memory poor" as compared with the Type 2 card). For this case of configuring only with Type 1 cards, the optimization procedure selected *very* small section sizes – smaller than one would think to be reasonable. We had to think about why this was happening; it went against our intuition. After some thought, we realized the reason – the objective of our optimization, afterall, was to *minimize consumed power, not to maximize processor efficiency*. The mathematical programming procedure had no regard for processor efficiency; its only concern was to use the available resources (in this case a lot of processors, and not much memory) to *minimize total consumed power*. If that means inefficient use of the processors, then so be it.

Consider why it is generally not optimal to force our expectations about what "reasonable" processor efficiencies should be for the case discussed in the previous paragraph. To achieve such efficiencies may require substantial memory (refer to Figure

2). So, if "reasonable" processor efficiencies are forced into the configuration, then the number of cards required by the configuration must increase – not because more *processors* are required, but because more *memory* is required. In fact, some processors will be idle while the few "efficient ones" are working away – the resource being fully used is the memory. Recall that consumed power is in direct proportion to the number of cards in the configuration. This helped us understand a new interpretation for what our optimization procedure was actually doing: piecing together the "pre-configured silicon" cards available in the most power efficient way possible. Forget about the importance of processor efficiencies that we study/teach in our parallel processing courses!

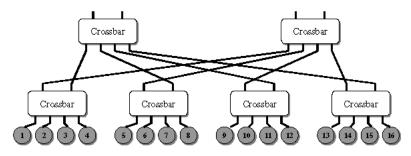

References [2B] and [3] further refine the results of [1A]. The most notable refinement involves the concept of configuring a compute node. In the Mercury system, a compute node (CN) is an entity on a daughtercard consisting of one or more compute elements (CEs). A compute element, in this context, is a SHARC® processor. In our study, the Type 1 cards were populated with CNs in which each CN contains 3 CEs; and the Type 2 cards were populated with CNs in which each CN contains 2 CEs. In [2B] and [3], we defined formulations to our optimization problem in which the utilization of each CN is determined by the optimization procedure.

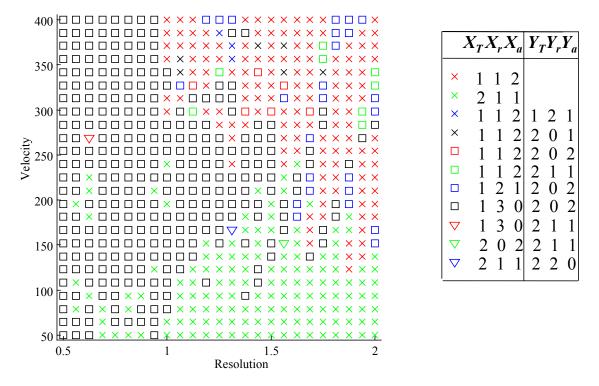

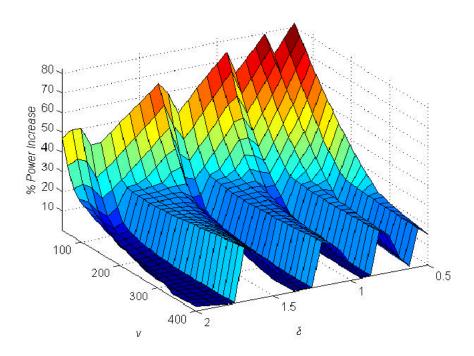

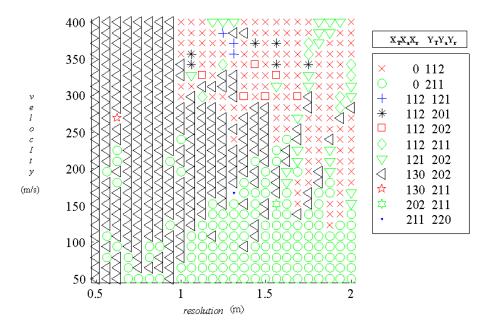

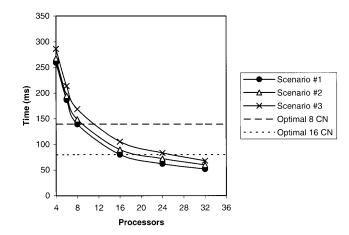

Figure 3 illustrates optimal configurations for a wide range of SAR operating points. The horizontal resolution axis represents the desired SAR image resolution in meters, and the vertical velocity axis is the speed of the vehicle (e.g., UAV) in meters/sec. The legend on the right side of the figure indicates two possible choices (X and Y) for CN configurations. The value of  $X_T$  and  $Y_T$  indicate the card Type (1 or 2) selected for the X and Y configurations. For example, the red square symbol ' $\Box$ ' is associated with the use of card Type 1 for the X configuration (i.e.,  $X_T = 1$ ) and card Type 2 for the Y configuration (i.e.,  $Y_T = 2$ ). Furthermore, for the X configuration, one CE (for each CN) is utilized for range processing (i.e.,  $X_r = 1$ ) and two CEs are used for azimuth processing (i.e.,  $X_a = 2$ ). Similarly, for the Y configuration, none of the CEs are used for range processing, and both CEs (for each CN) are used for azimuth processing (because  $Y_r = 0$ and  $Y_a = 2$ ). For the sake of comparison, consider now the configurations associated with the blue times symbol ' $\times$ ' where both the X and Y configurations use the Type 1 card, but the utilization of the CNs for X and Y are distinct. The number of configured CNs, and thus the total number of cards of each type, is also provided by the optimization procedure, but is not shown on Figure 3.

Although subtle, perhaps, this part of the work is extremely important because it cuts to the heart of a bigger issue. The most fundamental questions of interest for these types of systems should not necessarily be expressed in terms of processor efficiencies, or even processors or memories at all; what is important is the "configuration of the silicon," i.e., how can it be configured to minimize SWAP. The mixing of the two card types we studied is only a rough approximation to this general concept of "configurable silicon." With two discrete card types available, many, but not anywhere near all, possible combinations of processors and memories can be configured. But remember, processors and memory are not the only things we can build out of silicon. More specialized functional units can also be built. Parts 3 and 4 of this report deal with a key aspect of the project – namely, is it always necessary to configure silicon as discrete processor and memory modules? Could it be that silicon configurations consisting of modules or functional units less complex than processors and memories are also possible, and have superior SWAP characteristics in some situations? Before getting to the answers to these questions, the next part of this report deals with optimizing the SWAP performance of a multiprocessor implementation for STAP. Although Part 2 is similar to Part 1 in the sense that only processors and memories (and not reconfigurable computing) are assumed in the computing platform, the mechanism for minimizing SWAP in the STAP application centers around effective use of the interconnection network that supports interprocessor communication.

Figure 3. Optimal CN Configurations of the CN-constrained Model [2B].

## Part 2: Optimal Communication Scheduling for STAP

*Overview of References* [4*C*], [5*D*], [6*E*], [7], and [8]

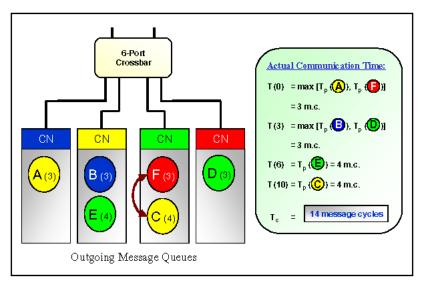

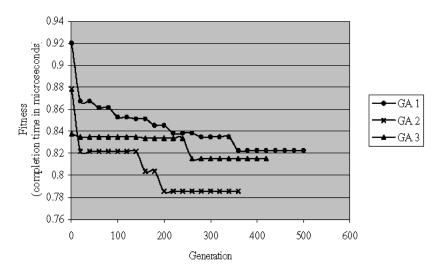

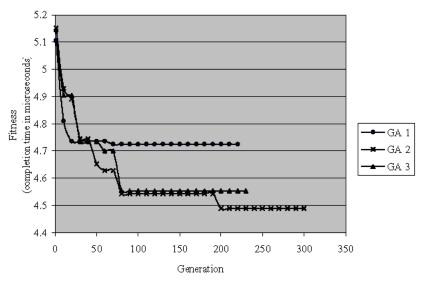

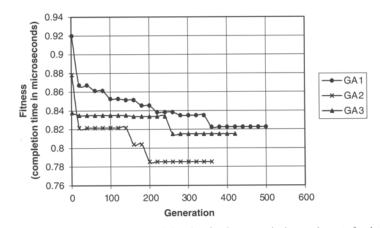

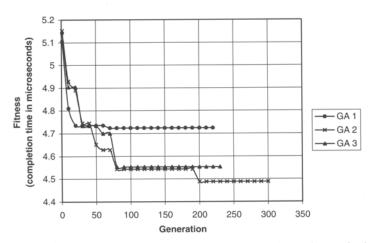

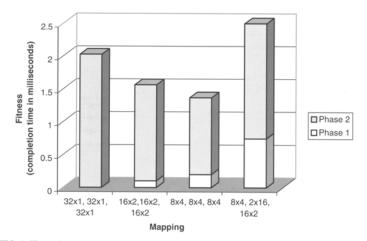

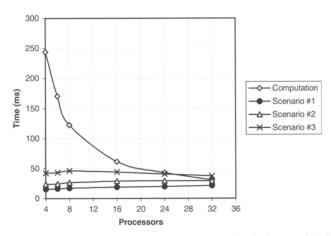

The work here develops and evaluates a genetic-algorithm-based (GA-based) optimization technique for the scheduling of messages for a class of parallel embedded signal processing techniques known as space-time adaptive processing (STAP). The GA-based optimization is performed off-line, resulting in static schedules for the compute nodes of the parallel system. These schedules are utilized for the on-line implementation of the parallel STAP application. The primary motivation and justification for devoting significant off-line effort to solving the formulated scheduling problem is the resulting reduction of hardware resources required for the actual on-line implementation. Studies illustrate that reductions in hardware requirements of around 50% can be achieved by employing the results of the proposed scheduling techniques. This reduction in hardware requirement is of critical importance for STAP, which is typically an airborne application in which the size, weight, and power consumption of the computational platform are often severely constrained.

For an application implemented on a parallel and embedded system to achieve required performance, it is important to effectively map the tasks of the application onto the processors in a way that reduces the volume of inter-processor communication traffic. It is also important to schedule the communication of the required message traffic in a manner that minimizes network contention so as to achieve the smallest possible communication times.

Mapping and scheduling can both – either independently or in combination – be cast as optimization problems, and optimizing mapping and scheduling objectives can be critical to the performance of the overall system. For embedded applications, great importance is often placed on determining minimal hardware requirements that can support a number of different application scenarios. This is because there are typically tight constraints on the amount of hardware that can be accommodated within the embedded platform. Using mappings and schedules that minimize the communication time of parallel and embedded applications can increase the overall efficiency of the parallel system, thus leading to reduced hardware requirements for a given set of application scenarios.

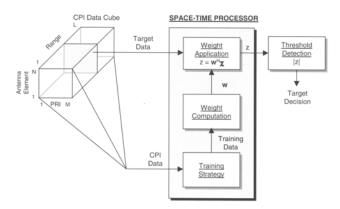

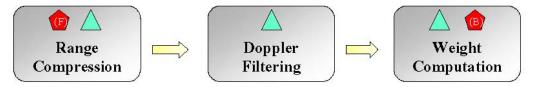

The work here focuses on using a GA-based approach to optimize the scheduling of messages for STAP algorithms. STAP is an adaptive signal processing method that simultaneously combines signals received from multiple elements of an antenna array (the spatial domain) and from multiple pulses (the temporal domain) of a coherent processing interval. The focus of this research assumes STAP is implemented using an element-space post-Doppler partially adaptive algorithm; refer to references [6E], [7], and [8] for details.

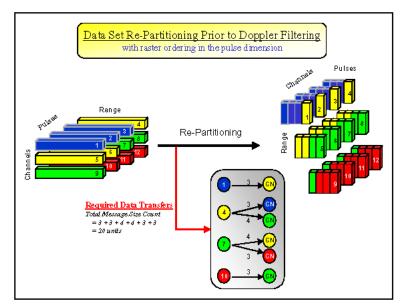

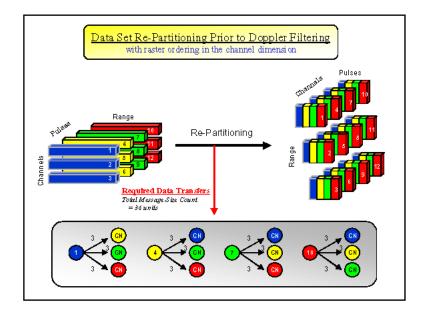

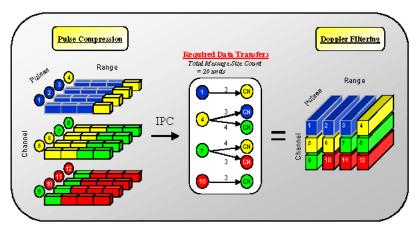

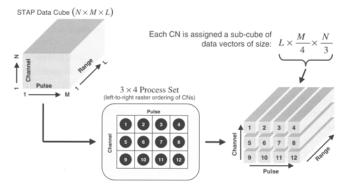

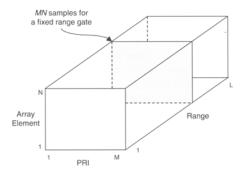

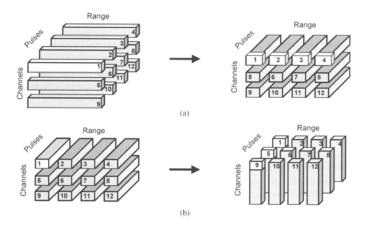

STAP involves signal processing methods that operate on data collected from a set of spatially distributed sensors over a given time interval. Signal returns are composed of range, pulse, and antenna-element digital samples; consequently, a three-dimensional (3-D) data cube naturally represents STAP data. A distributed memory multiprocessor

machine is assumed here for the parallel STAP implementation. The core processing requirement proceeds in three distinct phases of computation, one associated with each dimension of the STAP data cube. After each phase of processing, the data must be redistributed across the processors of the machine, which represents the communication requirements of this parallel application. Thus, there are two primary phases of interprocessor data communication required: one between the first and second phases of processing and one between the second and third phases of processing. After all three phases of processing are complete for a given STAP data cube, a new data cube is input into the parallel machine for processing.

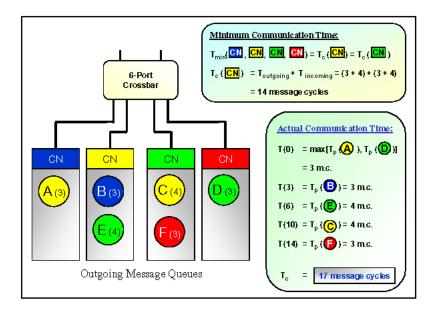

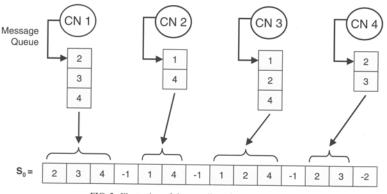

A proposed GA-based approach is used to solve the message-scheduling problem associated with each of the two phases of inter-processor data communication. This GA-based optimization is performed off-line, and the results of this optimization are static schedules for the compute nodes of the parallel system. These schedules are used within the on-line parallel STAP implementation. The results of the study show that significant improvements in communication time performance are possible using the proposed approach for scheduling. It is then shown that these improvements in communication time translate to reductions in required hardware for a class of scenarios. Performance of the mappings and schedules are evaluated based on a Mercury RACEway® network simulator developed under this project and described in references [4C] and [7].

For this work, the STAP data cube is partitioned into sub-cube bars of vectors where each vector is mapped onto a given CN (compute node), refer to [6E] for more details. A two-dimensional process set, as described in [8], defines the mapping of data onto CNs for each computational phase. Additionally, the process set defines the communication pattern for the required "distributed corner turns" of the STAP data cube.

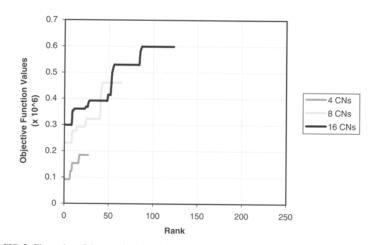

Summarizing the results published in [6E] and [8], it is demonstrated that off-line GAbased message scheduling can significantly improve the communication performance in a parallel system. When compared to baseline and randomly generated schedules, the GAbased schedules are significantly superior – typically reducing communication times by between 20% and 50%, see [8] for details.

Interestingly, it is shown that the best *mapping* – defined as a mapping that minimizes a mapping objective function – is not always the best choice in terms of minimizing overall communication time. In particular, as the number of CNs is increased, optimal mappings that require only one phase of communication generally report higher overall communication times than those good (but not optimal) mappings that require two non-trivial phases of communication.

The optimization of mapping and scheduling, either independently or in combination, is critical to the performance of the STAP application for embedded parallel systems. For such systems, great significance is placed on minimizing overall execution time, which includes both computation and communication components. Such reductions in execution time also translate into improved hardware efficiency and thus reduced hardware requirements, which is often critical.

Through extensive numerical studies, it is shown in [6E] and [8] that the GA-based optimization approaches can yield mappings and schedules that greatly improve the on-

line performance and reduce the hardware requirements of the parallel embedded system. Examples are provided that illustrate the optimal mapping and scheduling methodologies of [6E] and [8] can produce hardware savings of 50% and more when compared to typical solutions to the mapping and scheduling problems that might be employed by practitioners. Because of limitations on the size of problems that were executed/simulated, systems up to a size of only 32 processors were investigated. However, from the trends observed in overall completion times, it is apparent that even more significant savings in hardware/power requirements are realizable for STAP applications that require substantially larger systems having hundreds or even thousands of processors.

#### **Part 3: FPGA Power Prediction and Applications**

We discovered during the project period that predicting power consumption for an FPGA is a very difficult task. There were no commercially available tools that accurately predicted power consumption for any of the existing FPGAs. Thus, a major focus of this part of the work involved the development of accurate methods for predicting FPGA power consumption. References generated by this project in the area of power prediction include [9F], [10], and [11G], which are overviewed in Section 3.1.

In addition to trying to understand and predict FPGA power consumption, we also studied the types of computations that could be effectively mapped onto FPGAs. In theory, given enough gates, one could imagine configuring an FPGA board to behave as a microprocessor. Thus, again in theory, an FPGA board could be used to perform any type of calculation. However, based on the available technology, this would be extremely impractical. Our goal was to therefore use FPGAs to devise useful modules that are much less complex than a microprocessor, thereby reducing the SWAP overhead inherent when computations are performed only on microprocessors and/or DSPs. So, one of our aims was to characterize the types of computations that can be practically implemented in FPGAs. References produced in the area of mapping applications onto FPGAs include [12H], [13], [14], [15I], [16J], and [17], and these are overviewed in Section 3.2.

## **3.1 FPGA Power Prediction**

#### Overview of References [9F] and [10]

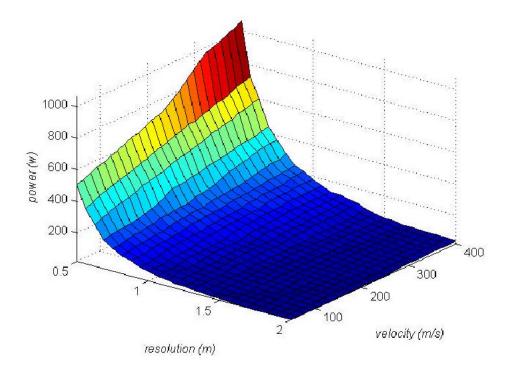

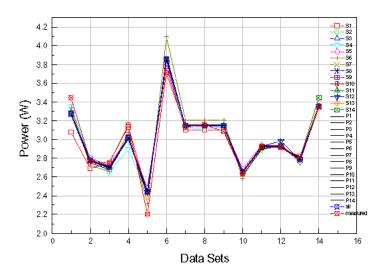

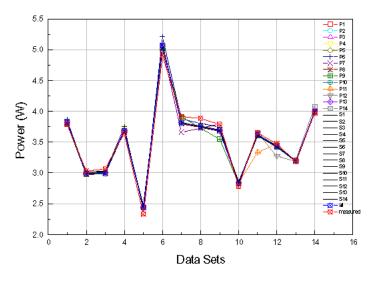

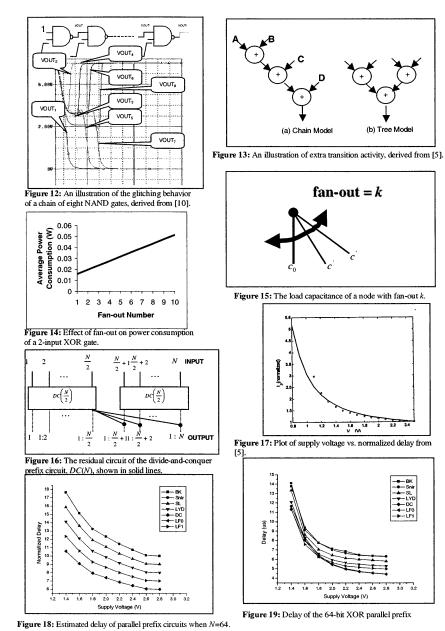

The work published in [9F] and [10] describes a practical and accurate power prediction tool for the Xilinx® 4000-series FPGA. The utility of the tool is that it enables FPGA circuit designers to evaluate the power consumption of their designs without resorting to the laborious and expensive empirical approach of instrumenting an FPGA board/chip and/or taking actual power consumption measurements. Preliminary evaluation of the tool indicates that an error of less than 5% is usually achieved when compared with actual physical measurements of power consumption.

The tool, which is implemented in Java, takes as input two files: (1) a *configuration file* associated with an FPGA design and (2) a *pin file* that characterizes the signal activities of the input data pins to the FPGA. The configuration file defines how each CLB (configurable logic block) is programmed and defines signal connections among the programmed CLBs. The configuration file is a text file that is generated using a Xilinx® M1 Foundation Series utility called *ncdread*. The pin file is also a text file, but is generated by the user. It contains a listing of pins that are associated with the input data for the configured FPGA circuit. For each pin number listed, probabilistic parameters are provided which characterize the signal activity for that pin.

Based on the two input files, the tool propagates the probabilistic information associated with the pins through a model of the FPGA configuration and calculates the activity of every internal signal associated with the configuration. The activity of an internal signal s, denoted  $a_s$ , is a value between zero and one and represents the signal's

relative frequency with respect to the frequency of the system clock, f. Thus, the average frequency of signal s is given by  $a_s f$ .

Computing the activities of the internal signals represents the bulk of computations performed by the tool. Given the probabilistic parameters for all input signals of a configured CLB, the probabilistic parameters of that CLB's output signals are determined using a mathematical transformation. Thus, the probabilistic information for the pin signals is transformed as it passes through the model of the configured logic, defined by the configuration file. However, the probabilistic parameters of some CLB inputs may not be initially known because they are not directly connected to pin signals, but instead are connected to the output of another CLB for which the output probabilistic parameters have not yet been computed (i.e., there is a feedback loop). For this reason, the tool applies an iterative approach to update the values for unknown signal parameters. The iteration process continues until convergence is reached, which means that the determined signal parameters are consistent based on the mathematical transformation that relates input and output signal parameter values, for every CLB.

The average power dissipation due to a signal *s* is modeled by  $\frac{1}{2} C_{d(s)}V^2a_s f$ , where d(s) is the Manhattan distance the signal *s* spans across the array of CLBs,  $C_{d(s)}$  is the equivalent capacitance seen by the signal *s*, and *V* is the voltage level of the FPGA device. The overall power consumption of the configured device is the sum of the power dissipated by all signals of the configured FPGA.

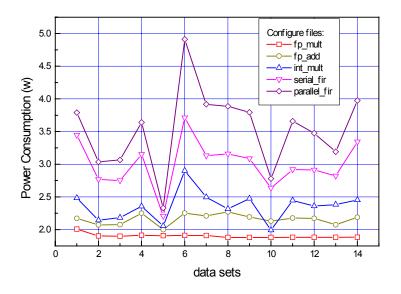

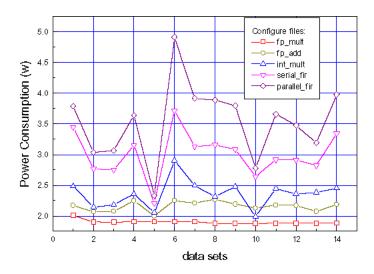

For the study conducted in [9F], a total of 70 power measurements were made using five different configuration files and fourteen different data sets. Descriptions of these configuration files and data sets are given in [9F]. Each of the configuration files used take a total of 32-bits of data as input. The first three configurations (fp\_mult, fp\_add, int\_mult) each take two 16-bit operands on each clock cycle, and the last two (serial\_fir and parallel\_fir) each take one 32-bit complex operand on each clock cycle. The 32 bits of input data are numbered as 0 through 31, and two key parameters are used to characterize these bits: an *activity factor, a* and a *probability factor, p*. As mentioned earlier, the activity factor of an input bit is a value between zero and one and represents the signal's relative frequency with respect to the frequency of the system clock, *f*. The probability factor of a bit represents the fraction of time that the bit has a value of one.

Figure 4 shows plots of the measured power for all combinations of the configuration files and data sets considered. For all cases, the clock was run at f = 30 MHz. With the exception of the fp\_mult configuration file, the most active data set file (number 6) is associated with the highest power consumption. Also, the least active data set file (number 5) is associated with the lowest power consumption across all configuration files. There is somewhat of a correlation between the number of components utilized by each configuration and the power consumption; however, it turned out that even though the serial\_fir implementation is slightly larger than parallel\_fir, it consumes less power. This is likely due to the fact that the parallel\_fir design requires a high fan-out (and thus high routing capacitance) to drive the parallel multipliers.

In addition to the graph shown in Figure 4, additional figures are provided in [9F] that overlay estimates of power consumption predicted by the tool developed in this project.

As mentioned above, predicted values of power were generally within 5% of actual measured values.

Figure 4. Measured power consumption of the configuration files and data sets from [9F].

## Overview of Reference [11G]

The method used by the above tool to compute signal activities was based on a previously published approach from another research group. That approach has some difficulties, primarily related to its time complexity. In [11G], a new analytical approach was developed by us for calculating signal activities. Our approach is based on a Markov chain signal model, and directly accounts for correlations present among the signals. We verified the accuracy of the approach by comparing signal activity values calculated using our approach with corresponding values produced through simulation studies. It was also demonstrated that the proposed approach is much more computationally efficient than competing approaches. In addition to describing the new approach for calculating signal activities, [11G] also provides a comprehensive review of past approaches, including the approach implemented for the tool described in [9F] and [10].

## **3.2 FPGA Applications**

## Overview of References [12H] and [13]

In references [12H] and [13], techniques for mapping portions of space-time adaptive processing (STAP) computations onto FPGAs are described. The output of STAP is a weighted sum of multiple radar returns, where the weights for each return in the sum are calculated adaptively and in real-time. The most computationally intensive portion of most STAP approaches is the calculation of the adaptive weight values, which typically

constitutes over 90% of all the computations needed in adaptive processing. Calculation of the weights involves solving a set of linear equations based on an estimate of the covariance matrix associated with the radar return data. The traditional approach for computing the adaptive weights is based on a direct method called QR-decomposition. This method has a fixed computational complexity, which depends on the size of the equation matrix and provides the exact solution. An alternative approach based on an iterative method called Conjugate Gradient was investigated, which allows for trading off accuracy for reduced computational complexity. The two approaches are analyzed and compared in [13]. The results show that the Conjugate Gradient approach can reduce the computations needed at the cost of reduced accuracy in some cases.

Existing computational strategies for STAP typically rely exclusively on the use of multiple DSPs and/or GPPs. An alternative strategy is proposed in [12H] and [13], which makes use of FPGAs as vector co-processors that perform inner product calculations. Two different "inner-product co-processor" designs are introduced for use with a host DSP or GPP. The first has a multiply-and accumulate structure and the second uses a reduction-style tree structure having two multipliers and an adder. For a fixed clock rate, the second design can provide a higher throughput, but requires more computation from the host (to perform the final summation of the partial sums).

In the work of [12H] and [13], the two inner-product co-processors were implemented using a block floating point format, which is much simpler to implement than standard floating point units. We also investigated overall accuracy of block floating point versus full floating point. It was demonstrated that the block floating point co-processors produce acceptable accuracy results for input data distributions that are uniformly distributed. Poor results are obtained, however, for cases where one or a few of the elements are much larger than the rest of the numbers. This is because the block-floatingpoint architecture normalizes all the exponents to the maximum exponent by shifting out the least significant bits of the mantissa so that all the exponents are equal, and then all the operations are integer arithmetic operations (based on the resulting mantissas), which are much easier to perform than general floating-point operations. The shifting out of the bits produces inaccuracy in the computations. For all the ranges of numbers considered, if the numbers are uniformly distributed, then the exponent distribution has an increasing exponential shape with a majority of the numbers close to the maximum value in the exponent domain. This results in a small number of bits from the mantissas of the numbers being shifted out, on the average. Another important point is that the multiply implementation uses a 15-bit mantissa, which implies that the mantissa of the input floating-point number is truncated to 15 bits from 23 bits, which itself introduces some inaccuracies.

#### Overview of Reference [14]

In reference [14], further studies of inner-product co-processor designs were conducted. In contrast to the inner product designs of [12H] and [13], which were based on a block floating point format, both floating point and integer formats were used in [14], both using 16-bit formats. The studies demonstrated that inner-product co-processors, for both integer and floating-point data, could fit into current (at that time) FPGA technology and achieve significant speed and throughput. The results of the implementations show that it is feasible and beneficial under certain circumstances to implement floating-point and integer operations in FPGAs (i.e., such as when a custom data format can be used, as with the SHARC® DSP which can convert back and forth between IEEE 32-Bit floating point and the SHARC® DSP 16-bit floating point formats).

The studies in [14] also considered the advantages and disadvantages of employing different degrees of pipelining in the inner product designs. One interesting (and somewhat counterintuitive) outcome related to pipelined versions of the designs was that adding more pipeline stages did not always allow for an increased clock speed at which the circuit could be executed. This was due to the fact that adding in the pipeline stages also added more overall complexity, which made it more difficult for the place-and-route routines of the FPGA design tool to find good implementations. Thus, as more pipelined stages were added, critical signal lengths sometimes increased, dictating that the clock rate actually had to be decreased. Estimates of power consumption were also evaluated for all designs considered in [14].

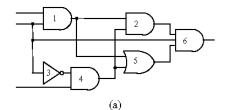

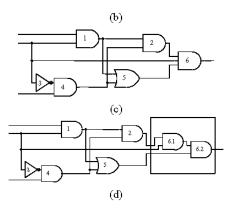

## Overview of Reference [151]

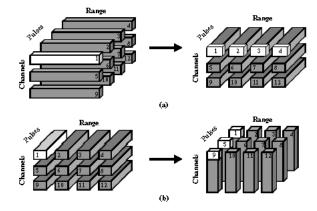

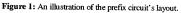

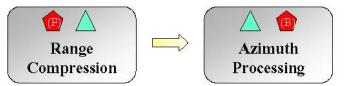

Two major contributions are presented in [151]. First, it is shown that the core computations from the SAR application, including both the range compression and azimuth processing phases, can be structured as a single deep computational pipeline that can be implemented directly on an array of FPGAs. Past results for high-throughput SAR processing (e.g., refer to [1A], [2B], and [3]) typically assume the computations are to be mapped onto a distributed memory multiprocessor system in which a subset of the available compute elements (CEs) is assigned to perform range processing and the remaining CEs perform azimuth processing. In this type of traditional approach, a number of processed range vectors are sent from the range CEs to the azimuth CEs where they are buffered in memory. After a prescribed number of compressed range vectors are present in the memory space of the azimuth CEs, azimuth processing commences on the azimuth CEs. Because of the significant intermediate buffer storage required by this approach, and the associated placing and fetching of data in this memory space by the range and azimuth CEs, respectively, this type of SAR implementation is generally not thought to be "purely streaming." However, as is presented in [15I], these computations (both phases) can in fact be structured as a single computational pipeline, which can be directly mapped onto an array of FPGAs.

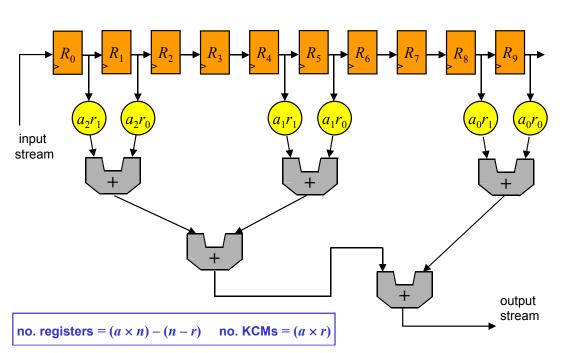

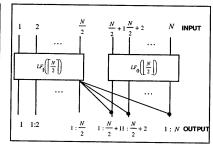

In the proposed approach, no intermediate memory buffer is required between the two phases of computation. Instead, within the structure of the computational pipeline are long segments of delay elements that effectively provide the intermediate storage associated with the more traditional approach. Figure 5 illustrates the structure of the computational pipeline. In the figure, small values of parameters are used for the purpose minimizing the size of the pipeline, while still illustrating its basic structure. Realistic parameters values would be on the order of thousands, resulting in a pipeline with millions of registers. Further details on sizing analysis and hardware comparisons between a deep pipeline implementation versus a multiprocessor implementation are provided in the online link to the presentation materials for reference [15I].

**Example:** no. range bins = n = 4 range kernel size = r = 2 azimuth kernel size = a = 3

Figure 5. Structure of the deep pipeline.

One potential advantage of the proposed approach is that data need not be continuously stored and then fetched from a separate memory module by CEs (which, incidentally, can require significant power consumption). Instead, the data streams continuously through a long computational pipeline. Within this pipeline are the taps of the FIR (finite impulse response) implementations of both the range and azimuth processing, interspersed with segments of delay elements. Although the resulting pipeline may be thousands of stages long for practical values of SAR parameters, it is a viable approach because end-to-end latencies on the order of 1 millisecond are typically acceptable, provided that the required throughput is achieved.

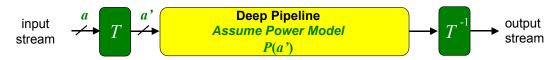

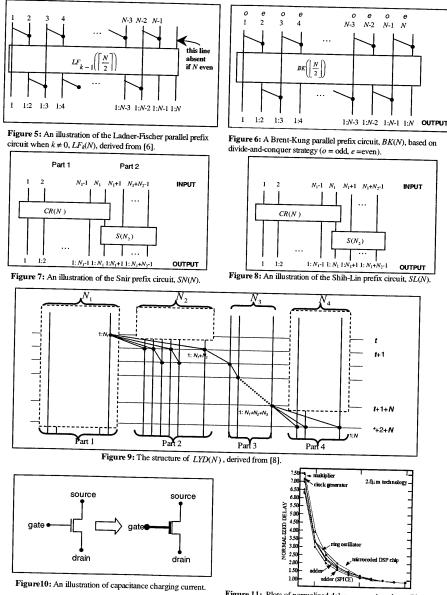

The second contribution presented in [15I] demonstrates how signal activity parameters of incoming data can be transformed, before the data are processed by a computational pipeline, as a means of reducing overall power consumption. The key to understanding this approach is the realization that the activity levels of the input signals to the computational pipeline dictate its level of power consumption. The activity of a given input signal (i.e., bit position) is defined as the fraction of time that the signal transitions relative to the system clock. We demonstrated that increasing/decreasing the signal activities of input data to a pipelined circuit implemented on an FPGA also increases/decreases the power consumption of the circuit. In [15I], we introduce a concept for how the activities of the input data can be transformed (pre-processed) so that the resulting (transformed) signals that are input into the computational pipeline have activity values that are well-matched with the pipelined circuit in terms of minimizing consumed power. At the end of the computational pipeline, an inverse transformation is applied to the output values to convert them back to their proper (and meaningful) representation. This concept is illustrated in Figure 6. The approach is based on two fundamental assumptions: (1) that the power consumption of the computational pipeline is significantly higher than that of the computational structures implemented to perform the transform and inverse transformation of the data and (2) that the computations performed within the computational pipeline are linear and time invariant.

Figure 6. Using activity transformations to minimize power consumption.

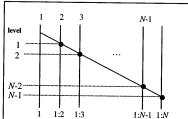

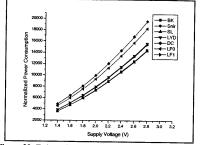

## Overview of References [16J] and [17]

References [16J] and [17] present a comparative study of different parallel prefix circuits from the point of view of power-speed trade-off. The prefix circuit plays an important role in many applications such as the carry-look-ahead adder, ranking, packing, and radix sort. The power consumption and the power-delay product of seven parallel prefix circuits were compared. By assuming a linear capacitance model, combined with PSpice<sup>®</sup> simulations, we investigated the power consumption in the parallel prefix circuits. The degrees of freedom studied include different parallel prefix architectures and voltage scaling. The results show that the use of the linear output capacitance assumption provides power estimates that are consistent with those obtained using PSpice® simulations. It was found that the divide-and-conquer prefix circuit, which is the fastest circuit considered, consumes the most power. Also - according to PSpice® simulations the power-delay product of the LYD (Lakshmivarahan-Yang-Dhall) prefix circuit was the best (i.e., lowest) among the circuits studied, while the power-delay product of the divide-and-conquer was the highest. This study demonstrates the importance of careful analysis of the speed-power trade-off when considering architectural choices for implementing a given computational function in hardware.

## Part 4: Hybrid FPGA/DSP/GPP Platform

## Overview of Reference [18K]

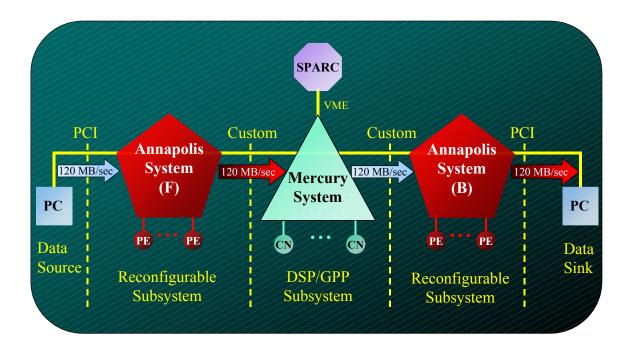

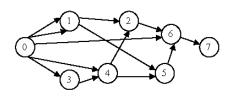

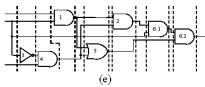

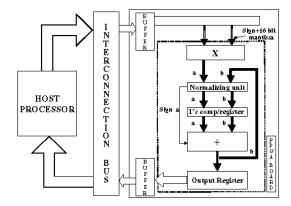

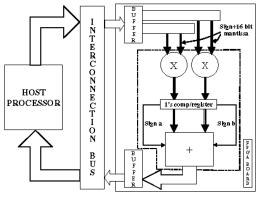

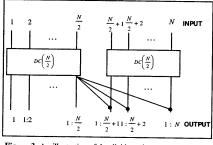

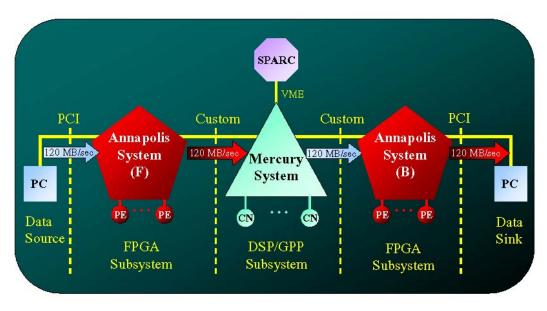

The prototype platform was developed to demonstrate the advantages and trade-offs associated with the combined use of different hardware technologies for two embedded radar-processing applications, namely SAR and STAP. The primary metrics of interest are size, weight, and power utilizations. The developed system can be configured with FPGAs, DSPs, and/or GPPs. Although the prototype system was not evaluated through fielded studies, experiments involving continuous input streams at relatively high rates were conducted in the laboratory using unprocessed radar data as input.

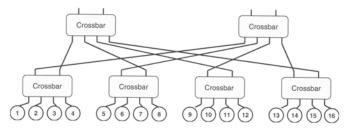

The FPGA components of the prototype system are commercially available WildOne<sup>TM</sup> and WildForce<sup>TM</sup> boards (from Annapolis Microsystems) populated with 4000-series Xilinx® parts. The WildForce<sup>TM</sup> boards each have four 4085-series FPGAs plus one control FPGA. The DSP/GPP components of the system are within a Mercury Race Multicomputer configured with both SHARC® and PowerPC® CNs. The Mercury system can be configured with up to eight PowerPC® nodes and eight SHARC® compute nodes (each SHARC® CN actually contains three SHARC® DSP chips).

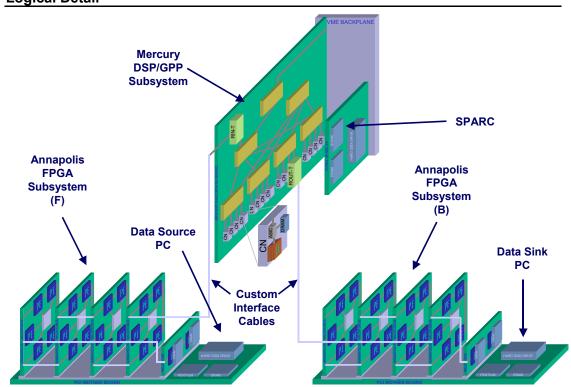

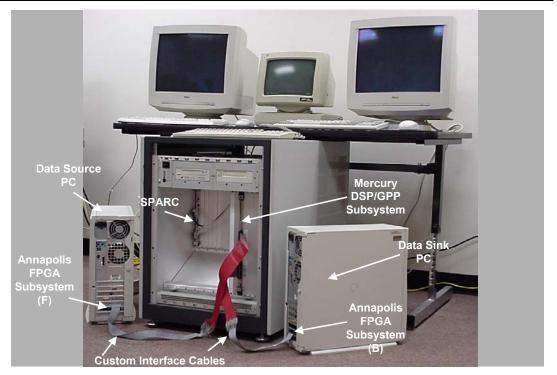

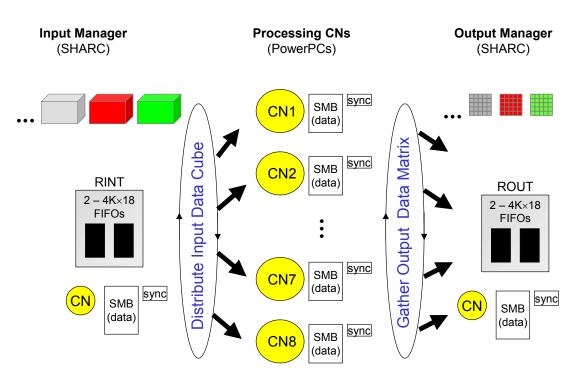

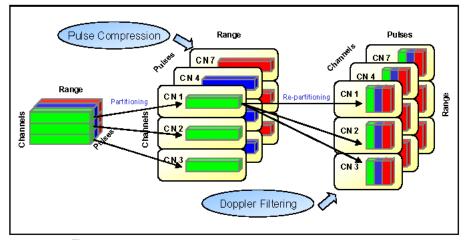

An overview of the overall architecture is depicted in Figure 7. A more detailed view of the major components of the hybrid system are illustrated in Figure 8, and a photograph of the actual prototype system is provided in Figure 9.

The source PC is responsible for initially loading unprocessed radar data (from disk) into a circular buffer within its main memory. Once the input data is loaded into the circular buffer, the source PC then continuously (and repeatedly) streams this data into the front-end FPGA subsystem, denoted as (F) in Figures 7, 8, and 9. It was necessary to locate the input data in a large main memory buffer in order to achieve realistic data throughput rates, which would otherwise not be possible if the data were streamed directly from the disk of the source PC. All of the Annapolis FPGA boards are PCI-based and reside on the data source and/or data sink PCs. A total of four WildForce<sup>TM</sup> boards are available, and zero or more of these may reside on the source and sink PCs. The source and sink PCs also contain one WildOne<sup>TM</sup> board each. The WildOne<sup>TM</sup> boards are not used for computation; they handle the data communication (through the PCI bus) between the PCs and the FPGA subsystems. The data communication among all FPGA boards is through two types of 36-bit wide connectors, one called systolic and one called SIMD.

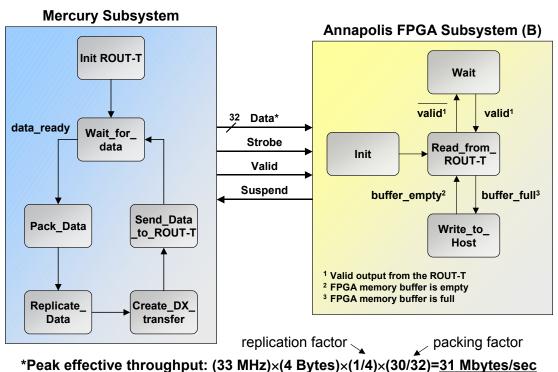

The data communication between the front-end FPGA subsystem (F) and the DSP/GPP subsystem is a custom interface developed using the systolic connector from Annapolis and the RIN-T input device from Mercury. Similarly, the data communication between the DSP/GPP subsystem and the back-end FPGA subsystem (B) is through a custom interface developed using the ROUT-T output device from Mercury and the systolic connector from Annapolis. More details on the design of the interfaces between the Mercury and the front- and back-end subsystems are provided in Figures 10 and 11, respectively.

# Hybrid FPGA/DSP/GPP Prototype Architecture

**Block Diagram**

Figure 7. Block diagram of the FPGA/DSP/GPP prototype architecture.

Design and implementation of the interface connecting the Mercury to the back-end FPGA subsystem (B), shown in Figure 11, was particularly challenging. The clock signal used to strobe the data from the Mercury was not programmable; it was fixed at 33 MHz. It turned out that the input impedance of the back-end FPGA subsystem was not very well matched with the output of the Mercury subsystem. As a result, the maximum clock rate possible was only about 8Mhz, or about one-fourth of fixed 33Mhz clock available. So, we implemented a scheme in which four copies each data word was transmitted from the Mercury, which effectively reduced the clock rate by a factor of four. We also had to include a packing scheme, which encoded two bits of each transmitted word to enable detection of the boundary between groups of copied data. This was necessary because the actual number of copies of each word received by the back-end GPGA subsystem was unpredictable, and varied between two and four. More details on this scheme can be found at the online link to the presentation materials for reference [18K].

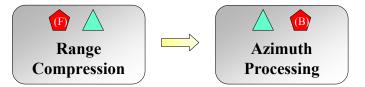

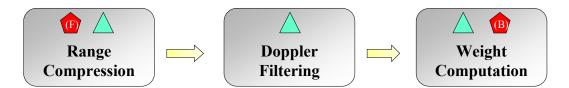

Figures 12 and 13 illustrate how the major computational components of the SAR and STAP applications can be mapped onto the prototype system. A candidate mapping is defined by assigning the computations of each major component to one or both of the symbols shown in each block (which correspond to one of the FPGA or DSP/GPP subsystems defined in Figure 7). Using SAR to illustrate, one mapping would be to

perform all of the range compression on the front-end FPGA subsystem (F) and then perform all azimuth processing on the DSP/GPP subsystem. Another possible mapping is defined by using the FPGA subsystems and the DSP/GPP for both components of computation. It is also possible to use only the DSP/GPP subsystem for both components of computations.

## Hybrid FPGA/DSP/GPP Prototype Architecture Logical Detail

Figure 8. Detail of the FPGA/DSP/GPP prototype architecture.

The SAR studies were designed by adapting the RASSP (Rapid Prototyping of Application Specific Signal Processors) benchmark developed originally by Lincoln Laboratory at MIT. The benchmark, which was originally implemented in serial C code, was first modified to execute on the parallel DSP/GPP subsystem. A data-streaming component was also added so that input data can be sent continuously from the data source of the prototype system. Core computations from the range compression and azimuth processing components were implemented for the FPGA subsystems, as described earlier in Part 3 of this report.

An overview of SAR processing flow is provided in Figure 14. The data distribution scheme for SAR is illustrated in Figure 15. For the case shown in the figure, a total of eight CNs were utilized: two SHARC® CNs (one for input and the other for output) and six PowerPC® CNs (two for range processing and four for azimuth processing). A detailed timing diagram is shown in Figure 16. Note from this figure that the processing

is well balanced and that the amount of idle time for each CN is relatively small. A summary of time and throughput results are provided in Figure 17. Note that the required input and output throughputs realized for this particular study, 0.71 Mbytes/sec and 1.42 Mbytes/sec, are well within the maximum capacity supported by the custom interfaces of 60 Mbytes/sec and 31 Mbytes/sec (refer to Figures 10 and 11). This implies that the constructed prototype system is capable of processing much more intensive instances of SAR processing.

## Hybrid FPGA/DSP/GPP Prototype Architecture Photograph

Figure 9. Photograph of the FPGA/DSP/GPP prototype architecture.

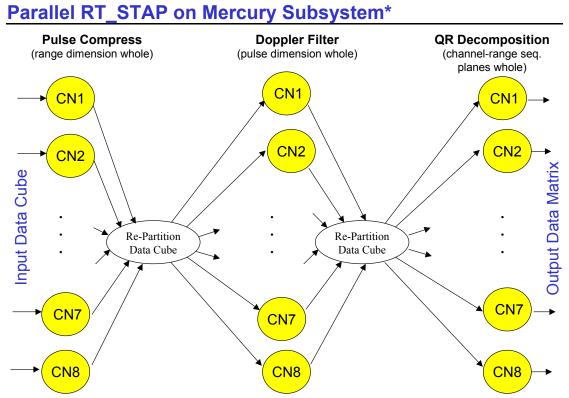

The STAP studies were designed by adapting the RT\_STAP (Real Time STAP) benchmark developed originally at the MITRE Corporation. This benchmark was already implemented for parallel execution on a PowerPC-based Mercury system. This implementation was expanded to also enable execution on SHARC® compute nodes. The same basic data streaming component that was developed for SAR was also adapted to enable the STAP input data to be sent continuously from the data source. Core computations from the range compression and weight computation components from the STAP processing flow were implemented for the FPGA subsystems.

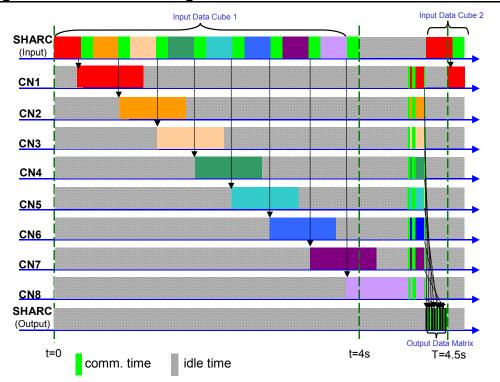

Similar to the figures associated with SAR, an overview of the scheme used to stream STAP processing is provided in Figure 18. Note from the figure that two SHARC® compute nodes are used for I/O and eight PowerPC® are used to actually perform the

STAP computations (for the particular instance of STAP considered). Unlike SAR, where CNs are dedicated exclusively to one particular phase of the computation, in the STAP implementation all CNs work on all three phases of computation. Figure 19 illustrates the three phases of computation required by STAP and the two communication phases (i.e., re-partitioning of the data cube) between the three phases. A space-time diagram is provided in Figure 20 followed by a summary of obtained throughput results in Figure 21. As was the case for SAR, note from Figure 21 that the required input and output throughputs realized for this particular study are well within the maximum capacity supported by our custom interfaces.

#### Mercury Subsystem Annapolis FPGA Subsystem (F) Init RIN-T Wait 32 Data\* suspend<sup>1</sup> suspend<sup>1</sup> Strobe not\_empty complete Wait\_for Write\_to\_ Valid data Init **RIN-T** Suspend buffer\_full<sup>2</sup> buffer\_empty<sup>3</sup> Determine Send Data Dest\_CN Read from Host <sup>1</sup> Suspend from the RIN-T <sup>2</sup> FPGA memory buffer is full Create DX <sup>3</sup> FPGA memory buffer is empty transfer

## Communication from Annapolis FPGA (F) to Mercury Interface Design

## \*Peak throughput achieved to date: (15 MHz) × (4 Bytes) = 60 Mbytes/sec

Figure 10. Interface Design: Communication from Annapolis FPGA (F) to Mercury.

# Communication from Mercury to Annapolis FPGA (B) Interface Design

Figure 11. Interface Design: Communication from Mercury to Annapolis FPGA (B).

Figure 12. Illustration of how the major computational components of SAR processing can be mapped onto the hybrid system.

Figure 13. Illustration of how the major computational components of STAP processing can be mapped onto the hybrid system.

# **SAR Processing Flow\***

\*Figure Derived from:T. Einstein, "Realtime Synthetic Aperture Radar Processing on the RACE Multicomputer," App. Note 203.0, Mercury Computing Sys, 1996.

Figure 14. Figure 14. SAR Processing Flow.

# Data Distribution for Parallel SAR Processing on Mercury Using 6 PPC CNs for Processing and 2 SHARC CNs for I/O

Figure 15. Data distribution for Parallel SAR Processing on Mercury.

Figure 16. Space-time diagram for streaming parallel SAR processing.

Figure 17. Throughput requirements achieved for streaming parallel SAR processing.

# Streaming Parallel RT\_STAP on Mercury Subsystem

Figure 18. Streaming parallel RT\_STAP on Mercury Subsystem.

\*Figure Derived from:M. Skalabrin and T. Einstein, "STAP Processing on Multiprocessor Systems: Distribution of 3-D Data Sets and Processor Allocation for Efficient Interprocessor Communication," ASAP Workshop, Mar. 1996.

Figure 19. Parallel RT\_STAP on Mercury Subsystem.

# Space-Time Diagram for Parallel RT\_STAP

Using 8 PPC CNs for Processing and 2 SHARC CNs for I/O

Figure 20. Space-time diagram for parallel RT\_STAP.

# Throughput Requirements for Medium Case Parallel RT\_STAP Using 8 PPC CNs for Processing and 2 SHARC CNs for I/O

|               | Samples (1920)                                | Function                                                            | Time                                                                                                  |